# **Footprint of AI in VLSI Design Automation**

## Anusha Anugu, Akshay Pittala

Department of Electronics & Communication Engineering, Jawaharlal Nehru Technological University, Kukatpally, Hyderabad, 500085 (Anushareddy.aenugu2410@gmail.com, pittalaakshay@gmail.com)

Abstract- This paper deals with the impact of Artificial Intelligence on the VLSI chip design techniques. An evident challenge ahead for the integrated circuits (IC) industry in the nano meter regime investigation. The splendid progress on VLSI technology and gradual shifting of VLSI chips designs to Ultra large scale integrated (ULSI) circuits system made the use of computer aided design (CAD) and programs(tool) helped significantly to the automation of VLSI chip design. Anyhow, by integrating and placing these tools together into one package, the functionalities and the effectiveness of CAD programs decreased drastically. To reduce these problem researchers suggested artificial intelligent techniques. Conventional methods employed for such tasks are mainly manual; thus becomes more time-consuming and resource-intensive. Artificial intelligence techniques like expert and knowledge-based systems, at first define the problem and then select the best solution from the different possible domains of solutions. Using AI algorithms in VLSI design and manufacturing them reduces the effort and time for processing and understanding the data across and within different abstraction levels by automated algorithms. Artificial Intelligence performance and their techniques used in aiming VLSI design for automation intelligence and high speed, and their efficient way of implementations are discussed in this paper.

Keywords- Artificial Intelligence, VLSI, ULSI, CAD, knowledge-based systems.

## I. INTRODUCTION

From the beginning of 1950's when first transistors are invented, the development of Integrated Circuit(IC) technology is focusing on integration of complex transistors into single chip. During the last thirty years, fabrication of IC technology went through four generations Small Scale Integration; Medium Scale Integration; Large Scale Integration; Very Large Scale Integration (VLSI) and yet furthering the IC technology to new era of Ultra Large Scale Integration (ULSI) However, the transition from tens and hundreds (SSI) of thousands of transistors and many more (MSI) cannot be accomplished manually. This is mainly due to the money and time constraints.

Eventually there is a rapid growth in IC's technology when compared to its compatibility in IC chip design. This is only reason due to the significant increase in growth of AI. In recent days, computer-based design tools are frequently handled and used by the knowledge obtained from the introduction courses from AI.

Earlier, many chips are designed by hand due to its larger size and they are very slow in performance. It is also become very difficult to verify them. These kinds of complexities are leading in development of an automation tool. This automation tools are upgraded for additional multiple tasks which are assigned for it. Chip designers brings new ways of designing in time to time basis like

combing the memory, new procedure in computational task which need to be automated in the design process. Companies like Intel, IBM have internal computer aided design (CAD) establishments for this purpose. Numerous companies like Cadence, Synopsis, and Mentor Graphics sell CAD tools, which are regarded as applications of Artificial Intelligence to chip design.

VLSI-computer-aided design (CAD) tools are involved in several stages of the chip design flow, from design entry to full-custom layouts. Design and performance evaluation of highly complex digital logic synthesis, layout synthesis, chip behaviour simulation, circuit simulation, optimization, and so forth and analogue ICs are dependent on the capability of the CAD tools involved.

Improvisation of VLSI–CAD tools is becoming increasingly challenging and complex with the tremendous increase in the number of transistors per chip. Numerous opportunities are available in the field of semiconductor and EDA technology for developing AI solutions to automate processes at various levels of VLSI design and manufacturing for quick convergence [1].

## II. LITERATURE REVIEW

The impact of AI on VLSI design was first demonstrated in 1985 by Robert. S. Kirk [2]. He briefly explained the scope and necessity for AI techniques in CAD tools at different levels of VLSI design. The advantages of

incorporating AI in the VLSI design process and its applications are briefed in [3].

**Khan et.al.** focused on the applications of AI in the IC industry, particularly in expert systems; different knowledge-based systems, such as design automation assistant, design advisor by NCR, being used in the VLSI industry [4]. Overall, these design advisors focus more on asynchronous CAD tools.

Khailany et. Al.[5] highlighted the application of AI in chip designing. They focused on AI-based approaches in the fields of microarchitectural design space exploration, power analysis, VLSI physical design, and analogue design to optimize the prediction speed and tape-out time. They proposed an AI driven physical design flow with a deep reinforcement learning (DRL) optimization loop to automatically explore the design space for high-quality physical floorplans, timing constraints, and placements, which can achieve better results, following clock-tree synthesis (CTS), and also routing steps. Rapp et. Al. presented a comprehensive presentation of state of the art on AI for CAD at different abstract levels.

The reviews mentioned above break down to provide a detailed discussion on the AI approaches proposed in the literature, mainly covering all the abstraction levels of the digital. VLSI design flow. In this review, we summarize the literature on AI algorithms for VLSI design and modelling at different abstraction levels.

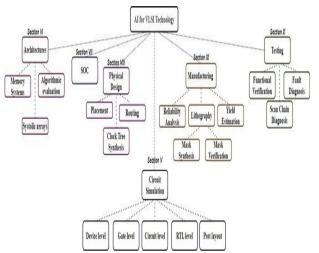

Fig 1. AI Implementation in different areas of VLSI Technology.

## **III.METHODOLOGY**

#### 1. VLSI Design Flow:

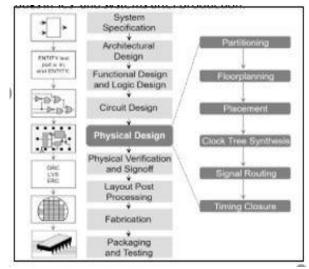

A traditional digital IC design flow has many hierarchical levels, as shown in Fig. 2; the flowchart covers a generalized design flow, including the front-end and backend of full-custom/semi-custom designs. The architectural design level comprises the basic architecture of the system

and includes decisions such as reduced instruction set computing/complex instruction set computing (RISC/CISC) processors and the number of arithmetic logic units (ALUs) and floating-point units. Behavioural design provides the functional description of the design often written using Verilog HDL/VHDL.

The timing information is checked and validated in RTL level of description. The logic synthesis tool checks that the gate-level netlist meets the area, timing, and power specifications. Logic verification is performed through testbench/simulation. Formal verification and scan insertion through design for testability (DFT) are performed at this stage to examine the RTL mapping [6].

Next, system partitioning, is performed followed by floor planning, placement, and routing. The place and route tool in the submodules, gates, and flip-flops, followed by CTS and reset routing.

After placement and routing, layout verification is performed to determine if the designed layout conforms to the electrical/physical design rules and source schematic. Then the resultant file is sent to the semiconductor foundries for IC fabrication. IC fabrication involves many advanced and complex physical and chemical processes. After the chip is fabricated, the wafer is diced and individual chips are separated.

Fig 2. VLSI Design Flow.

### 2. AI Algorithms and Tools:

AI provides the tools that are knowledge based which provides foundation and framework for problems. AI is a technology that enables a machine to simulate human behavior. AI can handle structured, semi-structured, and unstructured data. As it was mentioned in the above previous section, it is necessary to integrate all of the CAD programs tools levels into single one design environment. Hence, the use of AI automation helps to increase the CAD performance effectively.

AI tools for CAD VLSI systems which have been proposed and built are classified into three types:

- Synthesis Tools

- Evaluation / Analysis Tools

- Design Management System Tools

#### 3. Role of AI in VLSI Design:

AI is one of the most rising masterworks in the world of technology and innovation that helps to make computers are more reliable and easy to use.AI tools like KBES i, e, knowledge-based and expert systems provide the foundation and framework for problems on the way by first defining the problem and then selecting the best approach from the domain of different outcomes and possible solutions.

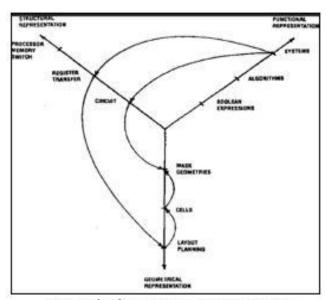

Fig.3 Role of AI in VLSI Designautomation

- **3.1 AI at the circuit simulation:** Simulation plays a major role in an IC device modelling. Performance evaluation of designed circuits through simulations is becoming increasingly challenging in the nano meter regime due to increasing process and environmental variations. The main ability is to discover electrical and functional performance variants early in the design cycle to increase the IC yield, it is also depending on the simulation of design tools.

- **3.2 AI at Architecture:** Design of VLSI architectures became dynamic with the evolution of AI techniques [7]. Most of the design development are motivated by the need for increased processing speed, improved reliability, and reduced implementation cost. The architectural designs proposed in the literature are based on the application domains of image processing, memory systems, signal processing, speech processing, systolic arrays, and microcomputer arrays.

- **3.3 AI at the SOC:** The FPGA in time basis became a robust device for accelerator hardware because of its

- high energy efficiency, low cost, reusability, and flexibility. The FPGA provide noteworthy advantages over microprocessors and DSP for high-performance and low-volume applications. The imperative argument for using FPGA as a reconfigurable hardware accelerator is that the commercially available FPGA still follow Moore's Law. FPGA offer parallelism as well as a flexible design. Joseph developed empirical models for processors using LR to characterize the relationship between processor response and micro-architectural parameters Jokie presents a complete end-to-end dual-engine SOC for face analysis that achieves >2X improvement in energy efficiency compared to the state-of-art systems.

- **3.4** AI in Physical Design: Here, we explore the impact of AI in physical design, which has many difficult combinational problems that are difficult to solve optimally. Over time, it has been observed that printing ever-small features on silicon with the earlier used 193-nm wavelength light introduces into the unprecedented levels of manufacturing challenges at the sub- micro meter and nanoscale technology nodes. In fact, physical design is one of the earliest areas of VLSI-CAD where AI was used [8]. Physical design can be broadly divided into four categories: partitioning, floor planning, placement, compaction. The main objective of partitioning is to divide the complex circuit into sub-blocks. Feature extraction is one of the most important aspects of implementing a AI model as it improve the accuracy and runtime of an AI model. Although the extensive application of AI algorithms has been performed on certain subcategories of physical design to improve the overallefficiency of the step in which

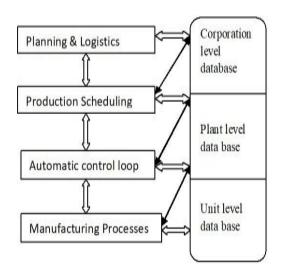

- 3.5 AI in Manufacturing: Employing AI algorithms in VLSI Design and manufacturing reduces the time and effort for understanding and processing the data within and across different abstraction levels via automated learning algorithms. Numerous semiconductor manufacturing processes are required when producing semiconductor products, including wafer preparation, epitaxy, oxidation, diffusion, ion implantation, lithography, etching, and metallization [9]. All the steps are performed in highly sophisticated fabrication units with constant human supervision

- **3.6 AI at Testing:** VLSI testing refers to the process of detecting possible manufacturing defects after chip fabrication. This is the most complex step in the VLSI design flow. The earlier a defect has been detected, the lesser the cost of final product, almost 70% of the design development time and resources are spent on VLSI testing.AI provides knowledge-based CAD tools to automate testing and verification of VLSI chip which is a complicated process [10].

Fig 4. Manufacturing Process.

## IV. RESULTS

Artificial Intelligence has the huge impact in VLSI design automation as AI algorithms involved to reduce the complexities by implementing knowledge based tools for testing and verification, it also reduces the production time, cost of production, size of chip, and provides the expert systems.

Heuristic knowledge have described few problems such as computationally inflexibility and ill-defined task for designing of new knowledge representation mainly methodology, CAD tool architectures, and new approaches in planning, search, and non-deterministic decision-making.

In the future, the advancements in differential programming and AI approaches can lead to inconceivable breakthroughs solutions in the EDA industry. The cost of testing a VLSI chip can be reduced using AI algorithms.

## V. DISCUSSIONS

This paper we have shown the use of Artificial intelligence in various aspects of VLSI Logical and Physical design like the use of AI in manufacturing, Circuit simulation, Design architectures, System on Chip, CAD tools.AI models prefers improved simulation rates when compared to basic EDA tools with better accuracy. Realization of AI learning algorithms in hardware enables reduction of the learning time and increases the speed of the prediction process.

A study showed that there are still some barriers with using of the CAD tools in an integrated form [11]. And also the CAD tools have not yet been designed to function together. Secondly, there are no mechanisms to automate and run the tools effectively; instead the designer must run

everything. Finally, the tools we use do not conform to a simple design representation, which contain a subdivision of all IC layouts that might satisfy the systems required specification of the design chip.

Therefore, the researches in CAD tools have started focusing on issues such as the adaptability of the design automation to different IC technologies, supporting higher level design specification, rather than building new CAD tool architectures [12].

## VI. CONCLUSION

Concluding, highlights of different designing environments for automation of VLSI design techniques have been introduced. Presently, the computationally efficient methods for estimating the corresponding outputs to the inputs are some of the areas attracting significant interest in the field of circuit modelling of VLSI–CAD. A vast network of AI is employed in the department of hardware acceleration to implement dynamic high-level digital circuits onto the hardware.

AI algorithms in hardware enables reduction of the learning time and increases the speed of the prediction process by many orders of magnitude .It could be beneficial to have benchmark datasets for AI training for future research and development of automated IC design flow. Such open source contributions in the VLSI community help to address the challenges more effectively. We expect to see an intelligent combination of EDA and ML in upcoming future for some bright results meeting the industrial standards.

## REFERENCE

- [1] C. K. C. Lee, "Deep learning creativity in EDA," in 2020 International Symposium on VLSI Design, Automation and Test (VLSI-DAT), pp. 1–1, 2020.

- [2] R. S. Kirk, "The impact of ai technology on VLSI design," in Managing Requirements Knowledge, International Workshop on, pp. 125–125, IEEE Computer Society, 1985.

- [3] G. Rabbat, "VLSI and ai are getting closer," IEEE Circuits and Devices Magazine, vol. 4, no. 1, pp. 15–18, 1988

- [4] M. Z. A. Khan, H. Saleem, and S. Afzal, "Application of VLSI in artificial intelligence,".

- [5] B. Khailany, H. Ren, S. Dai, S. Godil, B. Keller, R. Kirby, A. Klinefelter, R. Venkatesan, Y. Zhang, B. Catanzaro, et al., "Accelerating chip design with machine learning," IEEE Micro, vol. 40, no. 6, pp. 23–32, 2020.

- [6] L.-T. Wang, C.-W. Wu, and X. Wen, VLSI test principles and architectures: design for testability. Elsevier, 2006.

- [7] J. Zhang, Z. Wang, and N. Verma, "In-memory computation of a machine-learning classifier in a

# International Journal of Scientific Research & Engineering Trends

Volume 8, Issue 2, Mar-Apr-2022, ISSN (Online): 2395-566X

- standard 6t spam array," IEEE Journal of Solid-State Circuits, vol. 52, no. 4, pp. 915–924, 2017.

- [8] M. Sarrafzadeh and C. Wong, An introduction to VLSI physical design. McGraw-Hill Higher Education, 1996

- [9] L. Cheng, P. Gupta, and L. He, "Short papers efficient additive statistical leakage estimation."

- [10] S. M. Sze et al., VLSI technology. McGraw-hill, 1988

- [11] J. Carballo, W. J. Chan, P. A. Gargini, A. B. Kahng, and S. Nath, "Its 2.0: Toward a re-framing of the semiconductor technology roadmap," in 2014 IEEE 32nd International Conference on Computer Design (ICCD), pp. 139–146, 2014.