# A Review on Low Power and Less Area Multiplier Using Adder

M.Tech. Scholar Sarvesh Mani Pandey Asst. Prof. Anil Khandelwal

Department Electronics and Communication VNS Group of Institution Bhopal, MP., India

Abstract- Speed of the multiplier is highly dependent upon the number of partial products generated and the adder architecture used to add these partial products. The main intention of the paper is to use booth multiplier algorithm for designing the binary multiplier with the help of Ripple carry adder. The reason for using the booth's algorithm is that, using booth's algorithm we can reduce the number of partial products during multiplication. The adder here we have used is ripple carry adder. The viper here we have utilized is swell convey snake. This snake has an extremely straightforward engineering and is exceptionally simple to actualize. As here we are managing high bits, If we see generally speaking including the viper and stall's calculation we get a twofold multiplier which has nearly rapid on account of less halfway items and less power utilization as a result of the snake engineering we have utilized.

Keywords- VHDL code, Xilinx 14.1 ISE.

# I. INTRODUCTION

Adders assume essential job in numerous number-crunching calculations of PCs. Not only computers, but also used in processors for various operations where the increment of programmer counter be one of the example. It has almost become a requisite of most of the cognitive programmers and also considered as pliant. Usage of adders in any circuitry pares the excess number of transistors There are various adders[2] [1] [8] [14] invented so far like Ripple Carry Adder (RCA), Carry Look

Ahead

Adder (CLA), Carry increment Adder (CIA), Carry Skip Adder (CSKA) [13] [16], Carry Save Adder (CSA) [10], Carry Select Adder (CSLA) etc.

The simplest adder is the RCA. RCA contains full adder connected in parallel. Carry Look Ahead (CLA) is made after looking the lower bits and added if higher orders carry generated. The area and the delay is less than RCA because it has low number of gate .But it suffers from irregular layout. In Carry Save Adder three bit is added in parallel and carry is propagating through the stages.

In Carry Select Adder it Does the pre-calculation of all the conceivable convey, so the deferral is less. In any case, in every one of the adders CIA is best with respect to the Problems. Convey Increment Adder is set of two RAC squares of 4 bits. It has an Increment hinder with Half Adder (HA). There are some half and half Adders that have more power utilization and less deferral with respect to that of the adders. A portion of the adders are

CIA-RCA, CIA-CLA. This paper has taken into account the advantages of CSA and CSkA.

## II. LITERATURE SURVEY

N. Fahmina Afreen [1] Addition and Multiplication are two important mathematical operations that can be performed in every digital circuit. The performance of multiplier depends on adder, hence there is a need to use an efficient adder for multiplication. Definitely an efficient Adder can be utilized to enhance the performance of DSP system. This paper presents lower area, energy efficient 32-bit Array Multiplier based on optimized Carry Select Adder. The proposed Multiplier gives high-performance by saving 41% power, less delay by 27% with less area by reducing the slices up to 11.83% and LUTs by 7.6% when compared to conventional CSLA based Array Multiplier.

Sujan Sarkar et.al. Adders are the main components in digital designs not only in additions but also in filter designing, multiplexing, and division. The circuit performance depends on the design of base adder. The demand of high-performance VLSI (very large scale integration) systems is increasingly rapidly for used in small and portable devices. The speed of operation is depends on the delay of the basic adder and it is a very important parameter for high performance. There are so many research works have been so far done on the adder to reduce the delay of it. This paper have done comparative study of various parallel adders and proposed a hybrid adder circuit to improve the delay. Carry Save Adder (CSA) and Carry Skip Adder (CSkA) have been incorporated to improve propagation delay. The result

# International Journal of Scientific Research & Engineering Trends

Volume 5, Issue 4, July-Aug-2019, ISSN (Online): 2395-566X

shows the effectiveness for propagation delay improvement.

**K. Anirudh et,al,** Adders play a vital role in the digital signal processing systems. The design of 32-bit adders is of high importance because 32-bit architecture is common and widely used in many digital systems and processors. In this paper, the design and the implementation of various 32-bit adders like Ripple Carry Adder (RCA), Carry Increment adder (CINA) and Carry bypass adder (CBYA) for different full adder cells is done using the Verilog HDL. The results are obtained by executing Verilog code in Xilinx 14.5 ISE for the Spartan 3E family device with speed grade -5

Shaveta Thakral et.al. New technology innovation is facing a big challenge of miniaturization and low power electronics. Reversible logic proves to be an emerging solution. Reversible logic has various applications in modern low power computing environment. Adders play a ALU and processors role in computing environment. Adders are not only suitable for addition but for subtraction and multiplication also. For many commercial applications, decimal arithmetic is highly demanding BCD adders. Therefore reversible logic based BCD adders need to be designed for the implementation of ALU to add on high speed and low power requirements. The existing BCD adders are synthesized and simulated in Verilog using EDA (Electronic Design Automation) tool-Xilinx ISE design suit14.2. Finally the results are compared for all existing BCD adders in terms of total number of ancillary input lines. total number of garbage output lines, number and types of reversible logic gate used and their associated quantum cost.

**Bhavani Koyada et.al.**: In a digital circuit, the addition of certain number of bits is generic operation used in order to pare the complexity of the circuit and it operation. The selection of proper adder with requisite properties is more important for the efficient working of the circuit. Comparisons among different adders have been performed, which helps to reduce the laborious work. Adders that have been compared are all of 4 bit and have been synthesized using Xilinx synthesis tool and simulated using the Xilinx simulation tool.

The outcomes of synthesis reports and simulation of the circuit helps in finding out the different properties. For paradigm, the area consumed or the number of slices taken up by the circuit and speed can be calculated. These properties make out the difference in the operation and performances of the adders. The adders that have been compared, in this paper are Ripple Carry Adder, Carry Look Ahead Adder, Carry Save adder, Carry Skip Adder, Carry select adder, Modified Carry Select Adder and

Kogge Stone Adder based on two basic aspects namely, number of slices i.e., area occupied and speed.

Neelam Somani et.al 2016 Reversible logic has represented itself as a prominent technology which plays an important role in Quantum Computing. Theoretically Quantum Computers operates at high speed and consumes less power. Furthermore, Reversible logic can break the conventional speed of power trade-off. To prove this we are implementing Ripple Carry Adder and Carry Look Ahead Adder using reversible logic gates. The paper presents efficient adder circuits using Peres gate, New fault Tolerant gate and Double Feyman gate. The complexity, simulated outputs and the speed parameters for the Adder Circuit have been indicate during the Quartus II 9.1 edition and Model-sim tool .Moreover, the quantum algorithms can potentially solve NP-complete problems. Furthermore, doing high performance functions beyond the limit of deterministic computer systems is possible by only reversible logic. Quantum operations are unitary in nature which is reversible and hence the arithmetic operations like adders can be implemented using the reversible logic.

Omid Akbari1, Mehdi Kamal1,2et.al. 2016 In this paper, we propose a fast yet energy-efficient configurable approximate carry look-ahead adder (RAP-CLA). This snake has the capacity of exchanging between the surmised and accurate working modes making it appropriate for both mistake quiet and careful applications. The structure, which is more zone and power effective than best in class reconfigurable surmised adders, is accomplished by certain adjustments to the ordinary convey look forward viper (CLA).

The viability of the proposed RAP-CLA snake is assessed by contrasting its qualities with those of two best in class reconfigurable estimated adders just as the regular (precise) CLA in a 15nm Fin FET innovation. The outcomes uncover that, in the surmised working mode, the proposed 32-bit snake gives up to 55% and 28% deferral and power decreases contrasted with those of the precise CLA, separately, at the expense of up to 35.16% mistake rate.

It additionally gives up to 49% and 19% lower deferral and power utilization, individually, contrasted with other estimated adders considered in this work. At long last, the adequacy of the proposed viper on two picture handling uses of smoothing and honing is illustrated. The examination demonstrates that, all things considered, PSNR decreases of 12% and 16%, individually, might be accomplished by utilizing the proposed viper.

# III. RELALTED WORK

Volume 5, Issue 4, July-Aug-2019, ISSN (Online): 2395-566X

In most of the digital systems like computers or processors, there exists 32-bit architecture [5] such as 32bitintegers, registers, memory addresses etc. So the optimization of 32-bit adders reduces the total delay and hence speed increases [5]. In this paper, an attempt is made to design and compare the performance of different 32-bit adders using different full adder cells in the terms of slices, look up tables, delay and fan-out using VHDL language Xilinx ISE 14.1. In digital circuits, the arithmetic circuits are of high significance. Adders [1][2],[3],[4] play a vital role in the efficient implementation of the arithmetic circuit. All arithmetic operations can be implemented by using an adder circuit by following a suitable logic. An adder is a circuit that performs addition of two numbers and gives sum and carryout as results [4]. The basic adders cells used are the full adder and the half adder which add three and two inputs respectively [4]. There are many ways of implementation of full adder cell which are efficient than conventional full adder cell.

#### IV. PROPOSED WORK

The main of our thesis is to design a 32-bit multiplier by using either binary adder based on area, delay time and power required for the multiplier. Digital computer arithmetic is an aspect of logic design with the objective of developing appropriate algorithms in order to achieve an efficient utilization of the available hardware. The basic operation of additions implemented to the operation of multiplication. Multiplications and additions are most widely used arithmetic computations performed in all digital signal processing applications. In this thesis we are going to the performance of different adders implemented to the multipliers based on area and time needed for calculation.

#### V. METHODOLOGY

Multiplication may be a heavily used operation that figures conspicuously in signal process and scientific applications. Multiplication may be a terribly hardware intensive subject and thus we as users area unit largely involved with obtaining low-power, smaller space and better speed. a high speed processor depends significantly on the multiplier as it is one of the key hardware blocks in most digital signal processing systems as well as in general processors Modern IC Technology focuses on the planning of ICs considering additional space improvement and low power techniques.

The foremost necessary concern in classic multiplication largely accomplished by K-cycles of shifting and adding, is to hurry up underlying multi-operand addition of partial product. During this project we'll design the Booth multiplier using Ripple Carry Adder architecture. Additionally multipliers are designed for each radix-2 and radix-4. Results can show that the multiplier is able to multiply two 32 bit signed numbers and how this technique

reduces the number of partial products, which is an important factor to be achieved in this project.

## 1.Ripple Carry Adder (Rca)

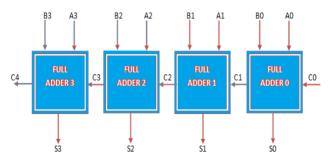

Ripple Carry Adder is a basic adder circuit which contains individual full adder cells and the carry generated upon addition is propagated between the respective adder cells[4]. The computation of result takes place only after the carry from the previous stage is applied as an input to present stage[4]. Due to these propagation delays, the delay is bound to occur which is a major disadvantage. Ripple Carry Adder adds 2 n-bit number plus carry input and gives n-bit sum and a carry output. The Main operation of Ripple Carry Adder is it ripple the each carry output to carry input of next single bit addition. Each single bit addition is performed with full Adder operation (A, B, Cin) input and (Sum, Cout) output. The 4-bit Ripple Carry Adder VHDL Code can be Easily Constructed by Port Mapping 4 Full Adder

Fig.1 Block diagram of ripple adder.

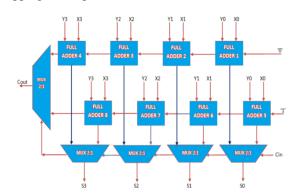

# 2. Carry Select Adder

Carry Select Adder VHDL Code can be constructed by implementing 2 stage Ripple Carry Adder and multiplexer circuit. Carry Select Adder select the sum and carry output from stage 1 ripple carry adder when carry input '0' and select Sum and carry output from stage 2 ripple carry adder, when carry input '1'.For the purpose of selecting sum and carry output, N+1 Multiplexer is implemented for N bit Addition Operation.4 Bit Carry Select Adder VHDL Code consist 2 numbers of 4- bit Ripple Carry Adder and 5 numbers of 2 to 1 Mux. For constructing Ripple carry Adder again implement Full Adder VHDL code using Port Mapping technique.

Volume 5, Issue 4, July-Aug-2019, ISSN (Online): 2395-566X

Fig.2 block diagram of carry select adder.

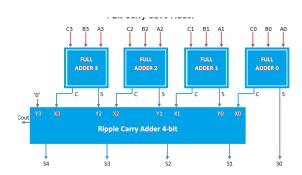

#### 3. Carry Save Adder

Carry save adder used to perform 3 bit addition at once. Here 3 bit input (A, B, C) is processed and converted to 2 bit output (S, C) at first stage. At first stage result carry is not propagated through addition operation. In order to generate carry, implemented ripple carry adder on stage 2 for carry propagation. Carry Save adder VHDL Code can be constructed by port mapping full adder VHDL Code to 2 stage adder circuit.

Fig.3 block diagram of carry save adder.

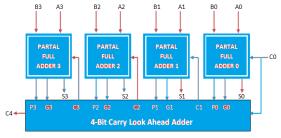

# 4. Carry Look Ahead Adder

Carry Look Ahead Adder is fastest adder compared to Ripple carry Adder. For the Purpose of carry Propagation, Carry look Ahead Adder constructs Partial Full Adder, Propagation and generation Carry block. It avoid Carry propagation through each adder. In order to implement Carry Look Ahead Adder, first implement Partial Full Adder and then Carry logic using Propagation and generation Block. Partial Full Adder consist of inputs (A, B, Cin) and Outputs (S, P, G) where P is Propagate Output and G is Generate output. VHDL code for carry look ahead adder can be implemented by first constructing Partial full adder block and port map them to four times and also implementing carry generation block as shown below

Fig.1 block diagram of look ahead adder.

# VI. CONCLUSION

In This paper, a 32 bit and 64 bit various adder in corporating new variable stage carry skip adder, look

ahead adder ,carry select adder, carry save adder has been designed to give the optimum performance in term of delay ,power and area The proposed asynchronous designs have the applications in digital circuits like a Timer/Counter, building reversible ALU, reversible processor etc.

# **REFERENCES**

- [1]. N. Fahmina Afreen Design And Implementation Of Area- DelayPower Efficient CSLA Based 32-Bit Array Multiplier 2017 2nd IEEE International Conference On Recent Trends in Electronics Information & Communication Technology (RTEICT), May 19-20, 2017, India 978-1-5090-3704-9/17/\$31.00 © 2017 IEEE

- [2]. Sujan Sarkar Design of Hybrid (CSA-CSkA) Adder for Improvement of Propagation Delay, Department of Electronics and Communication Engineering 978-1-5386-1931-5/17/\$31.00 ©2017 IEEE

- [3]. Kumar et.al.and Implementation of 32-Bit Adders Using Various Full Adders et.al International Conference on Innovations in Power and Advanced Computing Technologies [i-PACT2017] 978-1-5090-5682-8 /17/\$31.00 ©2017 IEEE

- [4]. Shaveta Thakral Comparative study and Implementation of BCD Adders for reversible logic based ALU2017 2nd International Conference on Telecommunication and Networks (TEL-NET 2017)

- [5]. Bhavani Koyada A Comparative Study on Adders 978-1-5090-4442-9/17/\$31.00 c 2017 IEEE, EEE WiSPNET 2017 conference.

- [6]. Neelam Somani. Chitrita Chaudhary, Sharad Yadav Reversible Adder Design For Ripple carry and Carry look ahead (4, 8, 16, 32-bit)—International Conference

- [7]. on Computing, Communication and Automation (ICCCA2016)

- [8]. Omid Akbari1, Mehdi Kamal1,2, Ali Afzali-Kusha1, Massoud Pedram3 RAP-CLA: A Reconfigurable Approximate Carry Look-Ahead Adder School of

- [9]. Electrical and Computer Engineering, University of Tehran, Iran 1549-7747 (c) 2016 IEEE.

- [10]. G. A. Clark, S. K. Mitra, and S. R. Parker, "Block implementation of adaptive digital filters," *IEEE Trans.* Circuits Syst., vol. 28, no. 6,pp. 584–592, Jun. 2014

- [11]. Singla,P and Malik,N.K,"A Cost Effective Design of Reversible programmable logic array"International Journal Of Computer Application ,vol.41,pp15,2012.

- [12]. Perkowski, M. and P. Kerntopf, "Reversible Logic. Invited tutorial" Proc. EURO-MICRO, Warsaw, Poland Sept 2001

- [13]. R. Feynman, "Quantum mechanical computers", Optical News, vol. 11, pp.11-2000

- [14]. A. Peres, "Reversible logic and quantum computers", Physical Review: A, vol. 32, Issue no. 6, pp. 3266-3276,2001