# An Enhanced Precision-Mitigated Area Parallel Architecture for 3D Multilevel Discrete Wavelet Transform

### **Lone Hameem Ul Islam**

Dept.of Electronics Engg. Punjab Technical University Jalandhar,Pujab,India lonehameem@yahoo.com

## **Azra Bilal**

Dept.of Electronics Engg. Punjab Technical University Jalandhar,Pujab,India Azra27nov@gmail.com

## **Prabhat Singh Lakhwal**

Dept.of Electronics Engg. UIET Chandigarh, PTU Jalandhar, Pujab, India lakhwalprabhat@gmail.com

Abstract-The paper presents parallelism-based architecture of executing 3D multi-level DWT (discrete wavelet transforms), that is efficient video frames and image algorithm of compression. The proposed architecture is one of the first parallelism along with pipelined architecture of 3-D DWT without group of image restriction. This architecture produced high throughput, reduced referencing of memory completely in temporal section, low latency and low consumption of power due to fetching of single row data flow, compared with those of previous reported works. This paper displays an enhanced precision mitigated area parallelism-based design for the unified implementation. The proposed architecture has been effectively implemented on Xilinx Virtex-VI series field-programmable gate array, offering a speed of 416 MHz, making it reasonable for real-time compression even with large frame dimensions. Besides, the architecture is completely scalable beyond the present coherent Daubechies filter bank. The proposed solution might be designed as lossy or lossless compression, in the field of 3D image compression framework, as indicated by the need of the client.

Keyword- DWT; DCT; RF; NDT

## I. INTRODUCTION

Compression methods are being quickly developed for huge information records, for example, images, where compression of data in applications of multimedia has become more essential. While the facts demonstrate that the cost of storage has decreased steadily, the measure of generated video and images data has expanded exponentially [1]. Image Compression is essential for some applications that include retrieval, transmission and huge storage of data for example video conferencing, medical imaging and documents. multimedia. Uncompressed images need significant transmission bandwidth and storage capacity. The goal of image compression method is to diminish image redundancy so as to be able to transmit and store data in an efficient form. This may result in the file size reduction and enables more images to be stored in a given measure of memory space or disk [2].

In applications, for example, telemedicine system, multispectral imaging and system of satellite imaging, lossless and lossy the two kinds of compression are essential, where less essential image and data thumbnails can experience lossy compression and medical data and high-resolution pictures can be compressed utilizing lossless DWT.Techniques of data compression depends on 2-D DWT (discrete wavelet transform) has gained

advantage over traditional JPEG based on DCT and is standardized in form such as JPEG2000 [3].DWT (Discrete wavelet transforms) is usually utilized for computer graphics, processing of videos and image analysis. As the algorithm of DWT is computationally intensive, implementations of VLSI algorithms usage are preferred for applications of real time [4]. The DWT can be partitioned into two classes - lossless and lossy DWT. The lossy DWT is generally utilized in situations which demand a high compression proportion; accordingly, it is exceptionally engaging in network distribution, HD satellite images, storage purposes, military and motion detection whereas lossless change is utilized in DNG (digital negative), images of medical and some digital cameras for image compression.

Be that as it may, as the coefficients of the lossy filter are real floating-point numbers, the computational complexity of implementation isvery high [5]. 3-D superset applications, i.e., 3-D-DWT on video, outperforms the current predictive coding standards, as MPEG 1-2,4, H.261-3 by rendering the quality highlights such as better PSNR, absence of blocky artifacts in low bit rates. Moreover, it has the additional provisions of exceedingly scalable compression, which is for the most part desired in present day communications over heterogeneous channels such as the Internet [6].3D-DWT is also

set of 3-D radio frequency (RF) data in ultrasonic systems, used in imaging applications for non-destructive testing (NDT) and quality control. The advent of 3D television and integral imaging for true autostereoscopic 3D visualization systems made the 3D DWT based lossy and lossless image processing and transmission an inseparable module in compression systems. This increased importance of 3-D DWT validates the need to find a high-speed and low power implementation of the 3D-DWT is additionally fundamental transmission or storing, compression of large set of 3-D (radio frequency) information in ultrasonic frameworks [7], utilized in imaging applications for nondestructive testing (NDT) and quality control [8]. The advent of integral imaging and 3D TV for genuine autostereoscopic 3D visualisation frameworks [9] made the 3D DWT based lossless and lossy processing of image and transmission an indistinguishable module in compression frameworks. In wavelet examination, the Discrete Wavelet Transform (DWT) breaks down a flag into an arrangement of commonly orthogonal wavelet premise capacities.

These capacities contrast from sinusoidal premise capacities. It is nonzero over just piece of the aggregate flag length. Here based on multi-dimensional discrete wavelets transform [10]. The Multi-Resolution Analysis (MRA) capability and timescale locality characteristics of the Discrete Wavelet Transform (DWT) have established it as a powerful tool for numerous applications, such as signal analysis, image compression and numerical analysis, as stated by Mallat (1989). This has led numerous research groups to develop algorithms and hardware architectures to implement the DWT [11]. The 3D wavelet decomposition is computed by applyingthree separate 1D transforms viewpoint images. The spatial wavelet decomposition on a single viewpoint is performed using the biorthogonal Cohen-Daubechies-Feauveau (CDF) 9/7 filter bank while the inter-viewpoint image decomposition onthe sequence is performed using the lifting scheme by means of the biorthogonal CDF 5/3 filter bank. All the resulting wavelet coefficients from the application of the 3D wavelet decomposition are arithmetic encoded [12].

Numerous modern applications require the datasets to process offline or online with various features and resolution. The fundamental algorithm of transform for JP3D is 3D DWT. It is a successful sub module in video coding, similar to Motion-JPEG, which is appeared to be more exact than MPEG-4 standard. The appearance of 3D and 4D medical imaging framework expanded the need of 3D volumetric compression of image system.

essential for compression, storing or transmission of large Preparing of 3D MRI pictures of mind through 3D DWT to extricate features for identification of Alzheimer's ailment and mild cognitive impairment in subjects. 3D DWT is likewise basic for transmission or storing of 3D RF of large sets information, compression in ultrasonic frameworks, utilized in imaging applications for NDT (non-dangerous testing) and quality control. The appearance of 3D TV and fundamental imaging for auto stereoscopic 3D representation frameworks made the 3D DWT based lossless and lossy transmission and processing of image in compression frameworks. The expanded significance of 3D Discrete wavelet transform approves the need to locate a rapid and low power execution of the equivalent.

> Bilateral Filtering is a nonlinear summation for smoothing an picture while keeping up edges and subtleties [13]. The vitality work is characterized by utilizing weighted minimum square dependent on standard, and a weighting capacity is characterized by a Gaussian dissemination. This technique can be stretched out into the joint twosided sifting [14] by utilizing guide flag.

Bilateral filter is denoted as BF and it is defined by:

$$BF[I]_{p} = \frac{1}{W_{n}} \sum G_{\sigma s}(\mid p-q\mid) \sum G_{\sigma t}(\mid I_{p}-I_{q}\mid) I_{q}^{\;(1)}$$

Where  $W_p$  is normalisation factor that ensures pixel weights sum to 1.0.

$$W_p = \sum G_{\sigma s}(|p-q|) \sum G_{\sigma t}(|I_p - I_q|)$$

(2)

Parameters  $\sigma_t$  and  $\sigma_s$  describe the amount of filtering for I image. Equation (1) is normalised weighted average as  $G_{\sigma s}$  is special Gaussian weighting which reduces the effect of distant pixels.  $G_{\sigma t}$  is a range Gaussian which reduces the effect of pixels q when their intensity values is different from  $I_n$

## II.THEORETICAL FRAMEWORK

The traditional implementation of the Discrete Wavelet Transform is done with convolution of the input having high pass(j) and low pass (i) channels. These channels are part into odd and even parts and are represented to as a

$$A[Z] = \begin{bmatrix} j_e(z) & j_o(z) \\ I_e(z) & I_o(z) \end{bmatrix}$$

(3)

where  $j_{\scriptscriptstyle e}$  and  $j_{\scriptscriptstyle o}$  are the even and odd parts of the high pass filter and  $I_{\rho}$  and  $I_{\rho}$  are the even and odd parts of the low pass filter It can be appeared that, given a pair of complementary filter (J, I), there dependably exist Laurent polynomials  $X_i(z)$  and  $Y_i(z)$ , and we can

factorize A[Z] so as to diminish the implementation complexity. The polyphase matrix is factorized into a series of lower and upper triangular matrix utilizing the scheme of lifting [12] as appeared as follows.

$$A[Z] = \prod_{i=1}^{N} \begin{bmatrix} 1 & X_i(z) \\ 0 & 1 \end{bmatrix} \begin{bmatrix} 1 & 0 \\ Y_i(z) & 1 \end{bmatrix} \begin{bmatrix} d & 0 \\ 0 & 1/d \end{bmatrix} (4)$$

where d is a constant and acts as a scaling factor. The CDF 9/7 filter bank can be represented by the following equations after the lifting scheme.

$$m_i^0 = y_{2i}$$

(Splitting)

$d_i^0 = y_{2i} + 1$

$d_i^1 = d_i^0 + \alpha \times (m_i^0 + m_{i+1}^0)$  (Estimated 1 E1)

$m_i^1 = m_i^0 + \beta \times (d_{i-1}^0 + d_1^0)$  (Improved 1 I1)

$d_2^i = d_i^1 + \gamma \times (m_i^1 + m_{i+1}^1)$  (Predict2P2) (5)

$m_2^i = m_i^1 + \tau \times (d_{i-1}^2 + d_i^2)$  (Update2 U2)

$m_i = k \times m_2^i$  (Scaling 1 m1)

$d_i = 1/k \times d_i^2$  (Scaling 2 m2)

In Equation (5), y is the input signal, m and d are the even and odd pixels/coefficients,  $\alpha$ ,  $\beta$ ,  $\gamma$  and  $\tau$  are the multiplication factors. The operations performed by the corresponding equations are named as Splitting, estimated 1 (E1), Update1 (U1), Predict2 (P2), improved 2 (I2), Scaling 1 (S1) and Scaling 2 (S2), as shown in Equation (3). For the LeGall 5/3 filter,  $\alpha = 1/2$ ,  $\beta = 1/4$ ,  $\gamma = \tau =$ 0. So the P2, U2, and Scaling operations are not necessary for LeGall 5/3 filter. For the CDF 9/7 filter,  $\alpha =$ -1.586134342. -0.05298011854.  $\gamma =$ 0.8829110762, 0.4435068522. K 1.149604398.

To deal with the truncation of the signs at limits, an extension of mirror is used by joining comparing changes into (5) toward the begin and stop of edge successions and at the singular edge limits and in addition for the 3-D changes. Presently, amid the calculation of 3-D wavelets, the request of spatial and transient change parts included can be exchanged where both the courses of action adjust to the meaning of 3-D-DWT.

Be that as it may, first transient and after that spatial (t + 2-D) change experience the ill effects of specific impediments with spatial adaptability or spatio-transient deterioration structure [15] which limit its future augmentations. Consequently, amid the structure of the present framework, first spatial and after that transient (2-D + t) deterioration are picked however in due prerequisite, the turnaround technique can be similarly

mapped into hardware without any difficulty. The conditions delineate the general case for the 1-D change. Be that as it may, at the edges of the frames in both the X-Y and Z bearings, uncommon thought is expected to apply the change.

In previous researches, the mirror augmentations, proposed in JPEG 2000 standard had been utilized. The conditions delineate the general case for the 1-D change. Since the wavelets utilized in DWT are detachable, the 1-D change can be utilized over and again to achieve 2-D furthermore, 3-D changes. For 2-D DWT [14], at first, the 1-D change is connected in the column bearing, i.e., on each line independently and the picture is isolated into two sub-groups relating to the low (L) and high (H) yields of the change.

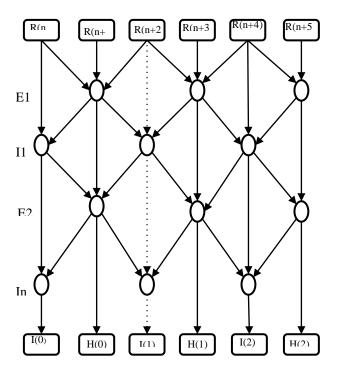

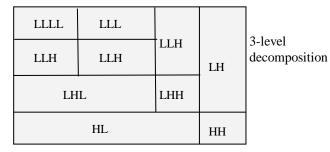

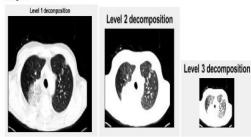

Figure 1 Flow Graph of signal after Flipping.

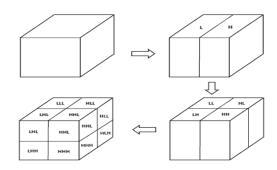

Figure 2 Volumetric Data on 3D DWT Level-1

Next, the 1-D change is connected to the yields of the past 1.Multi-Resolution Analysis change in the segment bearing. In this way, each of the two sub-groups of the picture is additionally partitioned into two more sub-groups. In this manner, the picture is currently isolated into 4 sub-groups (LL1, LH1, HL1, HH1), which is the 1 level 2-D change of the information picture. Similarly, the produced LL1 band is changed again to get the 2 level 2-D DWT. The LL2 band, created after the second change, ischanged again to accomplish the last 3 level 2-D DWT of the info picture. To perform 3-D DWT, the 3-D picture is cut along the Z-course. From that point forward, 2-D DWT is connected on each cut to get 4 sub-groups (LL1, LH1, HL1, HH1). At that point these yields are changed in the spatial or Z. bearing to partition each arrangement of cuts into 8 sub-groups (LLL1, LLH1, LHL1, LHH1, HLL1, HLH1, HHL1, HHH1). The LLL1 band is changed again to get the 2 level 3-D DWT. From that point onward, 1 level 3-D DWT is connected on the LLL2 band to get the last 3 level 3-D DWT yield. Figures 2 and 3 indicate how the picture is decayed when 1 level and 3 level 3-D DWT, separately, is connected in the line, section, and spatial bearings. Since the wavelets utilized in DWT are distinguishable, the 1-D change can be utilized over and over to achieve 3-D change.

At first, the 3-D picture is cut along the Z-bearing. From that point onward, the 1-D change is connected in the column heading, i.e., the 1-D change is connected on each line independently and on each cut in the 3D picture is isolated into two sub bands comparing to the low(L) and high(H) yields of the change. Next, the 1-D change is connected to the yields of the past change in the section bearing. Along these lines, every one of the two subgroups of the casing is additionally separated into two more sub-groups. Accordingly, each cut of the 3D picture is isolated into 4 sub-groups (LL, LH, HL, HH). At that point these yields are changed in the spatial or Z direction to partition each arrangement of cuts into 8 sub-groups (LLL, LLH, LHL, LHH, HLL, HLH, HHL, HHH).

Figures 2 and 3 demonstrate how the picture is decayed when 1 level and 3 level 3-D DWT, individually, is connected in the line, section, and spatial headings. After the change, the greater part of the vitality of the 3D pictures are amassed in the LLL sub-band of the 3D picture. Since the vast majority of the qualities in alternate parts of the 3D picture are close or equivalent to 0, a highpressure proportion can be acquired. The request of the change segments can be traded without influencing the last outcome. In the present structure first line section and after that spatial deterioration is performed while the switch strategy can be executed by rearranging the relating equipment squares however it will bring about an adjusting error.

One of the real preferred standpoints that DWT has over Discrete Cosine Transform (DCT) is that DWT permits multi-goals examination [13]. The recurrence goals can be expanded by applying the DWT on the low coefficients (L band). Multi-goals examination prompts a large portion of the vitality of the whole 3D picture being packed in a little piece of the casing. In this manner, higher the goals, the more noteworthy are the convergence of the vitality. In this paper, a 3-level examination has been performed on the 3D test picture. For 3-D DWT, the LLL (as a rule called LLL1) band is changed again to get the 2 level 3-D DWT. on the LLL2 band of this dimension 1 level 3-D DWT is connected to get the last 3 level 3-D DWT yield.

## III. PROPOSED ARCHITECTURE

## 1. Working Principle

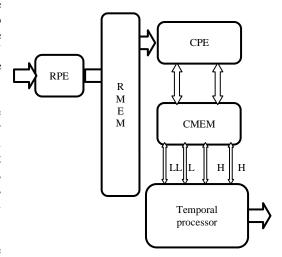

The multi-level 3D Discrete Wavelet Transform is obtained by processing the input through the Row Processing Unit (RPU), Column Processing Unit (CPU) which is composed of Spatial Processing Unit (SPU). Only two memory modules are employed to store the intermediate values in the processing, namely Row Memory Module (RMEM), Column Memory Module (CMEM), by abandoning TMEM and utilising hardware and software combination has produced better throughput than existing techniques. Figure 3 exhibits the proposed sweep based 1 level 3-DWT design with a square dimension representation of essential practical modules. Plainly from the figure, the proposed design does the spatial change first, pursued by its worldly partner. The accompanying two sections in this segment give a point by point see about connected at the hip working of the diverse utilitarian squares to understand those two change segments.

**2. Spatial Transform-** Scanning image frame row-wise with twofold clock, the approaching edges are fed to the spatial processor (SP) which change them two dimensionally with the assistance of two committed practical squares viz., the row processing element (RPE) and the column processing element (CPE). The checked pixels are at first sustained to RPE for column change. Then again, CPE remains inactive for the beginning edge in the frame succession till the underlying two columns are changed by RPE and the prepared coefficient squares are collected in line supports of line Memory module (RMEM).

Having a size of 2M/2 for a predefined outline estimate of M ×M, RMEM is enough space to the underlying two changed columns. As the changed coefficients from the third line leave RPE, section preparing initiates calculation all the while by getting low pass groups I<sub>0</sub> and  $I_1$  from the memory with the additional  $I_2$  band accessible on the web. In this stage, the empty RAM areas of I0 and

$I_1$  are doled out to  $I_2$  and  $h_2$  coefficient squares. In this manner, after fruition of the third line, the fourth one is sequentially handled, amid which the CPE gets occupied with the highpass groups of h<sub>0</sub>, h<sub>1</sub>, and h<sub>2</sub>, by bringing every one of them from the memory. As the h<sub>0</sub> and h<sub>1</sub> groups are not further used in calculation, the separate areas are ascribed to the capacity of 13 and h3 groups. The order is protected from now on, empowering the two components to work in flawless preparing synchronization while spatially changing each of the casings in arrangement.

Amid the calculation, CPE requires storage room for some transitory outcomes, which is advertised by 4M/2 profundity RAMs of column Memory module (CMEM). In this manner, the SP uses a general memory size of IOM/2. With the recently referenced twofold filtering, two pixels are encouraged into SP while two outcomes rise out of it in each clock cycle, which require an aggregate of (M<sub>2</sub>/2) cycles to finish the calculation of each casing. In the event that the casings have an even number of columns, both the handling components run easily with no intrusion amid the skip from one casing to the next. In any case, having an odd number of lines, the CPE needs to stay inactive for M/2 cycles (relating to one column) toward the start of each edge to get the first two columns prepared. Significantly, in the second occurrence as well, no additional clock cycles are spent by the SP to finish the calculation of individual casing. The Row MEM is implemented as four RAMs (R<sub>1</sub>, R<sub>2</sub>, R<sub>3</sub>, and R<sub>4</sub>) each having a size of M<sub>2</sub>.

Multiplexers are used to route the outputs of the Row processing unit to these RAM's and the outputs of the RAM's to the CPU. The inputs and outputs for the RMEM along with the RAMs in which inputs are fed into at that time against the current row processed, when the first row is processing, the low and high outputs of RPU (10, h0) are stored in  $R_1$  and  $R_2$ . Similarly,  $l_1$  and  $l_1$  are stored in  $l_2$  and  $l_3$  and  $l_4$  respectively.

Row processing element block processes the row and give output as L and H signals. These signals are correct for reading when output signal valid is correct. Column processing block, further process the row coming as input (L andH), and provides output as (Il\_out, hh\_out, h\_out, hl\_out). Another internal signals s as Il\_mem. lh\_mem, hh\_mem, hl\_mem is used to store the processed data in memory.

**3. Temporal Transform**- The changed casings, to be deteriorated accordingly in the transient area, are fundamentally put away in two double port casing cradles of column MEmory module (CMEM), as appeared in proposed architecture. With two such starting outlines previously put away, and the third one drawing nearer, the

worldly processor (TP) begins figuring the last change segment of 3-D-DWT. While at each cycle, two pixels of past two edges are perused out from CMEM cradles for the calculation, the particular areas are used for the reposition of two approaching pixels of the present edge.

By the calculation requires increasingly; one pixel of the third edge is to be perused out again from memory at single clock rate, which can be satisfied through the usage of the second port of the double port RAMs. Subsequently, the transient preparing continues inside and out while the RAM areas are revived in a nonstop way and in the wake of passing a N2 clock cycles, the present period of the calculation is finished. Moreover, the CMEM supports are completely topped off with the pixels of the third and fourth edges. In the precise next cycle, the comparing activities of the following stage begin in a comparable way with the worldly processor getting occupied with the calculation of the third, fourth, and fifth casings. From the CPE throughput is being stored in CMEM via two ports of LH and HH band of frames. LH and HH port are treated as the lower and higher nibble of the data respectively. further these bands of data are fetched from the CMEM via four ports of LL,LH, HL and HH. Four frequency data is being processed in the temporal process as discussed in the above section. The final throughput has been achieved using this hardware and firmware software. Firmware software is being utilised to write the output in file by reading output ports. firmware is required to control high speed image processing operations in the real time, moreover utilisation of the firmware provides implementation of workstation use model and that support easy extensions and modifications

Figure 3 Proposed enhanced Architecture.

It is assumed that proposed architecture accepts the information from external RAM that is persistently refreshed with new edges. In row wise manner, the input is read at both the negative and positive edges of the

clock. As the architecture does not require the existence HLH, HHL,.....) which needs to be sampled at "valid" of the entire sequence beforehand image of 3-D. it tends to be utilized in real time processing. Aside from the edges, the design takes a control signal and clock signal to show the transform expected to perform. In Enhanced architecture we have used the parallelism along with pipelining to achieve maximum results and for best results we have proposed to use the hardware and software embedded solution. As our architecture is giving output in pipelined parallel format so we can remove the bottleneck and heavy memory like TMEM. And use the firmware software to write the output in file by reading output ports.

## 4. RPE and the RMEM

Among all the small-scale structures for various sub modules, which change the information of the frame in three ways, the RPE module is the easiest. As depicted in Fig. 3, it is a direct usage of (5) with pipelining connected to accelerate the activities. Filtered with a double clock, the approaching pixels are isolated into progressive pairs of odd and indeed, even ones at the SPLITTER stage and push ahead in parallel all through the pipeline. The required data path tasks of lifting are performed upon these pixels at back to back estimated (Ei), improved (Ii), and Shift (Si) phases of the RPE (as delineated in Fig. 3), at the end delivers sets of high pass and low pass pixels accessible from the ports OUT EVEN and OUT ODD in a streamlined manner.

These pixels, preceding segment handling, incidentally put in RMEM which produce synchronized information stream to store and also feed the coefficients to CPE. Subsequent to handling the underlying two columns of an edge the changed coefficients totally top off the memory areas as delineated. At the precise next clock cycle, two new pixels viz., I(2,0) and h(2,0), touch base from RPE and they are put at the areas of R1 and R3 (allude to depiction 2), which are simply left empty as put away information, in particular, I(0,0) and I(1,0) are perused out at the initiation of section preparing.

Resulting areas are likewise invigorated till every one of the coefficients from column 2 are put away in those two RAMs. So also, amid preparing of the following line, RAMs R2 and R4 experience a progression of memory refreshments as the areas beforehand containing h0 and h1 coefficient squares are ascribed to the capacity of coefficients of h3 and I3, accessible from RPE. In this way, an occasional example can be distinguished among the revived RAM sets, which are further given in a forbidden frame against the handled lines.

TP reads the inputs coming for CPE output signals (ll\_out, hh\_out, lh\_out, hl\_out) and process them to further level and gives output as (LLL, LLH, LHL, HHH,

signal. The memory in the proposed architecture is free from any such situation where the RAM assets would be pointlessly possessed with stale information which are not to be utilized for future calculation.

## IV.INVESTIGATION OF SFG TO FACILITATE PARALLEL **COMPUTATION**

The issues related with planning designs for section and fleeting directional changes are anyway basic. In a setup where frames are filtered push astute and handled coefficients from RPE are separated adjacently in lines, the segment processor needs to sit tight for a whole line to get another information test for handling and the worldly processor needs to keep down for the whole casing before it can continue with the following calculation step. In the same way as other flag handling models, the 3-D-DWT processor therefore characteristically conveys enormous memory and inertness overhead in its working guideline. Obviously, a pipelined configuration like RPE does not fit in for segment and worldly preparing and parallel structures are for the most part tried to address this issue. The by and large preferred standpoint of any DWT processor lies in tending to these execution bottlenecks effectively.

## V.IMPLEMENTATION AND RESULTS

## 1. Multipliers and Data path Precisions.

After the subtleties of the engineering and the information the executive's standards have been completely chalked out, the issues identified with mapping the plan into a reconfigurable gadget are of prime intrigue. These incorporate the exactness of the multipliers in the design. Being unreasonable numbers, the flipping coefficients relating to (4) are not in a perfect world feasible in engineering with the equipment multipliers. Rather, those numbers could be considered up to a limited exactness amid structuring. Be that as it may, the effects of this restricted accuracy are knowledgeable about brought down PSNR values and ensuing corruption of the nature of duplicated frames amid the decompression.

Also, the exactness of the information tests directly after every multiplier influences the PSNR in a very comparable manner. These realities demonstrate to an exchange off between the moderate equipment spending plan, which increments straightly with exactness and the frame quality. In this manner, recreations are done to quantify the impacts of those two parameters after which particular coefficient and partial information exactness of 11 and 2 bits are repaired to accomplish great video quality at similarly low equipment limitations. The separate hard multipliers are planned through " shift-n-

add" mechanism and pipelined to speed up the processing.

## 2. Implementation Results

The engineering has been mapped into Xilinx programmable device (FPGA) XC4VFX140 with speed review of 12 through the Xilinx ISE 7.1i device. A uniform word length of 17 bits has been kept up all through the processor to bear the cost of adequate information profundity.

Table 1 Parameters of proposed technique

| Parameter               | Project               |

|-------------------------|-----------------------|

| Custom frame size       | 128x128               |

| Group of frames (GOP)   | Infinite              |

| Maximum clock           | 582 MHz               |

| frequency               |                       |

| Throughput Two          | Initial latency 2N2 + |

| results/cycle           | 2Nψ + 47 clock cycles |

| Number of occupied      | 163                   |

| slices                  |                       |

| Total number four input | 411                   |

| LUTs                    |                       |

| Number of block RAMs    | 6                     |

| Power                   | 1.57mW                |

Subsequent to pipelining the multipliers, the basic way for the processor comprises of single viper, making it very quick. A quick counter-based controller was structured which handles all the location age and other exchanging tasks at the fast of primary information way.

Such controllers are programmable and can synchronize the control flag age as indicated by various video outline sizes. So other than standard N  $\times$  M, they can deal with standard quarter normal middle configuration or regular halfway organization or on the other hand different distinctive perspective proportions. The adders from the library and gadget double port square RAMs have been used as the essential assets for the structured processor. Reenactment is performed by ModelSim XE III 6.0a, which yields a lot of final products totally coordinating the outcomes from MATLAB 2017b, where a model of the equipment is made.

Table2 Comparison of the proposed technique with Existing Works.

|                                              | Q. Dai et<br>al.[26] | M.<br>Weeks<br>et al.©1<br>[27] | B. Das<br>et al.<br>[28] | J. Xu et<br>al.[29]           | Z. Taghavi<br>et al. [30] | Proposed        |

|----------------------------------------------|----------------------|---------------------------------|--------------------------|-------------------------------|---------------------------|-----------------|

| Design type                                  | Complete<br>3-D      | Complet<br>e<br>3-D             | Compl<br>ete<br>3-D      | Tempo<br>ral<br>process<br>or | Temporal<br>processor     | Complete<br>3 D |

| Filter bank                                  | For D-9/7            | l-length                        | D-4D-<br>9/7             | D-9/7                         | For D-9/7                 | For D-9/7       |

| Multipliers                                  | 24*8                 | -                               | Nil                      | -                             |                           | Nil             |

| 1 level<br>computing<br>time for P<br>frames | ,                    |                                 | •                        | (P +<br>4)N2                  | (P + 4)N2                 | 2N2 +<br>P/2N2  |

| Throughput                                   |                      | -                               | •                        | 1res/cy<br>cle                | 1res/cycle                | 2res/cycle      |

| Hardware<br>utilization                      | -                    | -                               | 100%                     | -                             | -                         | 100%            |

| GOP (P)                                      | P=32(ma<br>x)        | 32(max)                         | Infinite                 | Infinite                      | Infinite                  | Infinite        |

## 3. Performance Evolution

Table 3. Parameters

| Parameter                 | Project                    |

|---------------------------|----------------------------|

| Custom frame size         | 64x64                      |

| Group of frames (GOP)     | Na                         |

| Maximum clock frequency   | 582 MHz                    |

| Throughput Two            | Initial latency 2N2 +      |

| results/cycle             | $2N\psi + 47$ clock cycles |

| Number of occupied slices | 148                        |

| Total number four input   | 378                        |

| LUTs                      |                            |

| Number of block RAMs      | 6                          |

| Power                     | 1.57mW                     |

Power: 1.57W

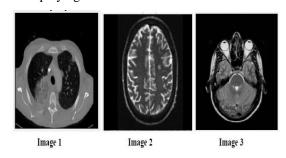

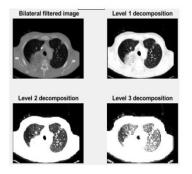

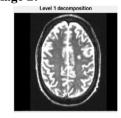

**4. Images used as input:** Here we have considered three images of different contrast and dimensions. 1st image dimensions are 64\*64, 2nd image dimensions are 128\*128 and third Image dimensions are 256\*256. All the images different in the size as well as in the quality, due to which we have achieved different values for PSNR while employing bilateral filter.

Figure 5 Image 1 as input

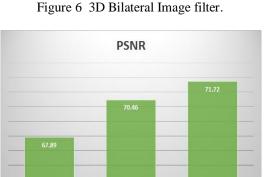

**5. 3D Bilateral Image filter-** Bilateral Image filter has been employed to enhance the image employed for the compression. We have considered three-dimensional filter here.

Figure7: PSNR for three sample images **Multi-level DWT**

LLLH

Original 3D

1-level decomposition

2-level decomposition

Figure 8 Multi level DWT.

Three level DWT decomposition of filtered image and LL31 shows the lowest frequency sub band and HH11 shows the highest frequency sub band. Let us consider each image one by one to perform Multi-level DWT; each decomposition level is depicted below:

## Image 1:

Image 1:

Figure 9: Multilevel DWT of Image 1

Image 2:

Figure 9 Multilevel DWT of Image 2

## Image 3:

Level 2 decomposition

Figure 10 Multilevel DWT of Image 3

Table 5 compression ratio of the images

| Image 1   | image 2   | image3   |

|-----------|-----------|----------|

| 64*64     | 128*128   | 256*256  |

| 47.8:4.59 | 65.4:4.20 | 105:6.57 |

## 5.2 Comparison with Existing Technique

Table 6 comparison between existing and proposed technique

| Parameter                    | Existing                                       | proposed                                       |

|------------------------------|------------------------------------------------|------------------------------------------------|

| Custom frame size            | 256x256                                        | 256x256                                        |

| Group of frames (GOP)        | Infinite                                       | Infinite                                       |

| Maximum clock frequency      | 321 MHz                                        | 450 MHz                                        |

| Throughput Two results/cycle | Initial latency 2N2 + 2N\psi + 47 clock cycles | Initial latency 2N2 + 2N\psi + 47 clock cycles |

| Number of occupied slices    | 1776                                           | 154                                            |

| Total number four input LUTs | 2188                                           | 416                                            |

| Number of block<br>RAMs      | 350                                            | 6                                              |

| power                        |                                                | 1.57W                                          |

### VI.CONCLUSION

In this paper of combination hardware and software combination have been utilised, firmware software has been employed to write the output in file by reading output ports, proposed architecture has been enhanced by employing parallelism along with pipelining to achieve maximum throughput. In the proposed architecture heavy memory elements are eliminated like TMEM, resulted in the area mitigation. The throughput produced in term of area, power and frequency is better than existing techniques. Heavy compression ratio can be noted from the table 4.4 for all the medical images. furthermore, proposed architecture reduced memory referencing and related low power consumption, low latency, and high throughput compared to those of earlier reported works. In future scope Multilevel DWT compression can be combined with the algorithmic approach to attained controlled compression over each frame depending on the attributes of the respective frame.

## REFERENCES

- [1] Siddeq MM, Rodrigues MA. A novel 2D image compression algorithm based on two levels DWT and DCT transforms with enhanced minimize-matrix-size algorithm for high resolution structured light 3D surface reconstruction. 3D Research. 2015 Sep 1;6(3):26.

- [2] Chowdhury MM, Khatun A. Image compression using discrete wavelet transform. International Journal of Computer Science Issues (IJCSI). 2012 Jul 1;9(4):327.

- [3] Das A, Hazra A, Banerjee S. An efficient architecture for 3-D discrete wavelet transform. IEEE Transactions on circuits and systems for video technology. 2010 Feb;20(2):286-96.

- [4] Biswas R, Malreddy SR, Banerjee S. A High-Precision Low-Area Unified Architecture for Lossy and Lossless 3D Multi-Level Discrete Wavelet Transform. IEEE Transactions on Circuits and Systems for Video Technology. 2018 Sep;28(9):2386-96.

- [5] Hu Y, Jong CC. A memory-efficient scalable architecture for lifting-based discrete wavelet transform. IEEE Transactions on Circuits and Systems II: Express Briefs. 2013 Aug;60(8):502-6.

- [6] J.-R. Ohm, M. van der Schaar, and J. W. Woods, "Interframe wavelet coding: Motion picture representation for universal scalability," J. Signal Process. Image Commun., vol. 19, no. 9, pp. 877– 908, Oct. 2004.

- [7] P. Govindan, and J. Saniie," Processing algorithms for three-dimensional data compression of ultrasonic radio frequency signals," Signal Processing, IET, 9(3), pp.267-276, 2015.

- [8] A. Katunin, M. Daczak, and P. Kostka, "Automated identification and classification of internal defects in

- composite structures using computed tomography and 3D wavelet analysis", Archives of Civil and Mechanical Engineering, 15(2), pp.436-448, 2015.

- [9] A. Aggoun, "Compression of 3D Integral Images Using 3D Wavelet Transform", Journal of Display Technology, vol. 7, no. 11, pp.586-592, Nov. 2011.

- [10] R.Sivakumar and Dr. E. Mohan, "High Resolution Satellite Image Enhancement Using Discrete Wavelet Transform", International Journal of Applied Engineering Research, Volume 13, Number 11 (2018) pp. 9811-9815.

- [11] Satyendra Tripathi, Bharat Mishra, "Three Stage 2-D Discrete Wavelet Transform using Modified Vedic Multiplier", 2017 7th International Conference on Communication Systems and Network Technologies.

- [12] Amar Aggoun,, "Compression of 3D Integral Images Using 3D Wavelet Transform", JOURNAL OF DISPLAY TECHNOLOGY, VOL. 7, NO. 11, NOVEMBER 2011.

- [13] C. Tomasi and R. Manduchi, "Bilateral filtering for gray and color images," in Proc. IEEE ICCV, 1998, pp. 839–846.

- [14] J. Kopf, M. F. Cohen, D. Lischinski, and M. Uyttendaele, "Joint bilateral upsampling," in Proc. ACM SIGGRAPH, 2007, p. 96.

- [15] M. Elad, "On the origin of the bilateral filter and ways to improve it," IEEE Trans. Image Process., vol. 11, no. 10, pp. 1141–1151, Oct. 2002

Lone Hameem Ul Islam received B. Tech in Electronics and communication engineering from Gulzar Institute of Engineering & Technology affiliated to PTU Jalandhar, India in 2016. He got

interest in the field of research and worked in Grian Technology Pvt Ltd in Bengaluru and Chanakya Research as research engineering for image processing projects. He persuaded M-Tech in Electronics and communication engineering from Universal Institute of engineering and technology.

**Azra Bilal** received B.E in electronics and communication engineering from SSM college of science and technology affiliated to Kashmir University, India in 2017. She persuaded M- Tech in Electronics and

communication engineering from Universal Institute of engineering and technology.